Main content

Top content

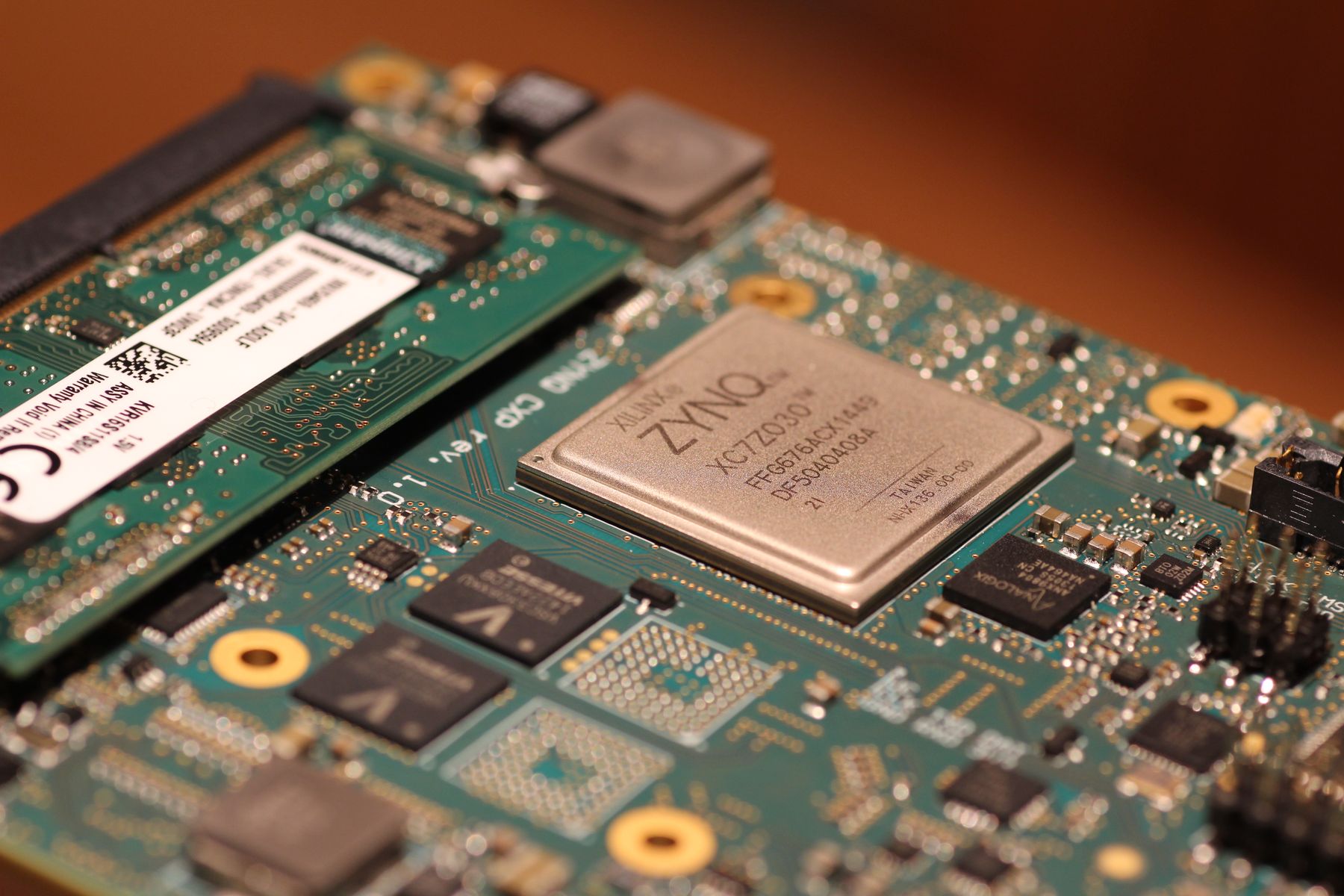

Reconfigurable and Parallel Computer Architectures

Rekonfigurierbare und parallele Rechnerarchitekturen (in German)

The lecture deals with the architecture and application of reconfigurable computer systems. Reconfigurability refers to the possibility of changing hardware function blocks and their interconnection. This way, the available resources can be adapted to varying application requirements. Different approaches for reconfiguration and the resulting architectures are discussed - from fine-granular architectures based on field-programmable gate arrays (FPGAs) to coarse-granular architectures that allow complex modules, such as arithmetic units, to be interconnected. Of particular interest are methods that enable dynamic, partial reconfiguration. Dynamic reconfigurability describes the possibility to reconfigure a system at runtime. If a system can be partially reconfigured, its internal structure can also be changed partially. An additional focus is on massively parallel architectures such as on-chip multiprocessors and graphics processors.

The design methodologies that are introduced in the lecture are practically used in the exercises by applying state-of-the-art design tools. In particular, the students learn how to use high-level design tools that enable hardware realizations based on specifications in C/C++ and OpenCL. Of particular interest are the advantages and disadvantages of the different methods with regard to required design time and achieved resource efficiency.